# Digital System Design IAIK Open Flow

**DSD** Team

06.03.2024

Digital System Design Graz University of Technology

# Introduction

#### **Motivation**

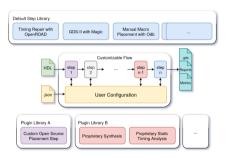

With the recent release of several open source Process Design Kits (PDKs) such as SKY130 and advances in open source EDA tools, it is now possible to design manufacturable chips without the need to sign NDAs.

This document shows how to use the IAIK Open Flow to develop, test and integrate your cipher into a chip.

The goal of the IAIK Open Flow is to provide students with the tools and framework to develop their cipher locally on their own computer.

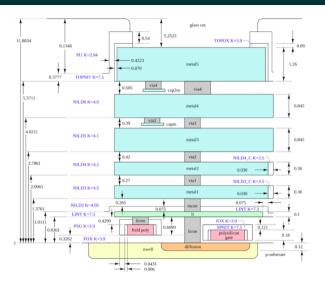

### Sky130 Stackup

Layer Stackup Sky130

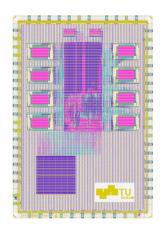

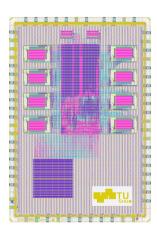

#### **Open Flow ASIC**

- · Acts as a harness for your cipher

- · SoC with Ibex RISC-V Core

- 8 kB ROM

- 16 kB SRAM

- · Various peripherals

- Repository: open-flow-asic

Open Flow ASIC

#### **Open Flow Docker**

- · Container with open source tools

- Make sure to install docker

- List of tools: open-flow-docker

- Pull the image via:

```

$ docker pull \

extgit.iaik.tugraz.at:8443/\

sesys/iaik-open-flow/open-flow-docker

```

#### **Open Flow Template**

- Your working template for the DSD course

- Tasks are split into

- ex1/ Files for exercise 1: cipher\_core

- ex2/ Files for exercise 2: cipher\_peripheral

- open-flow/tapeout/ Integration into harness

- Repository: open-flow-template

#### **General Procedure**

- The Open Flow ASIC has already been pre-hardened

- For now, a placeholder-macro is used instead of your cipher

- Your goal: Create your cipher in 1000x1000 um

- · Communicate with the SoC over bus interfaces

- · Harden your cipher as a hard macro

- Replace the empty wrapper in the final tapeout step

- This solution was chosen so that development of your cipher is possible on lightweight hardware such as laptops

## Exercise 1

#### **Cipher Core - Sources**

- All source files under ex1/

- ex1/src/ RTL files

- ex1/tb/ testbench

- open-flow/ex1\_aux/config.json

- config for OL2

- open-flow/ex1\_aux/pins.cfg

- pin config for OL2

#### **Cipher Core - Output**

- Output directories

- results/ex1\_runs/

- OL2 output files

- results/ex1\_macro/

- Most recent OL2 output

- ex1/tb/sim\_build/

- Simulation output

#### **Make Targets**

- ex1-lint

- ex1-openlane

- ex1-openroad

- ex1-klayout

- ex1-cocotb

- ex1-cocotb-gl

To add additional source files to your cipher, just place them into the src/ folder! All files ending in .sv are automatically picked up for the implementation and the simulation.

ex1/src/\*.sv

#### **Exercise 2**

#### **Cipher Peripheral - Sources**

- All source files under ex2/

- ex2/src/ RTL files

- ex2/tb/ testbench

- ex2/sw/ software for the ibex core

- open-flow/ex2\_aux/config.json

- config for OL2

#### **Cipher Peripheral - Output**

- Output directories

- results/ex2\_runs/

- OL2 output files

- results/ex2\_macro/

- Most recent OL2 output

- ex2/tb/sim\_build/

- Simulation output

#### **Make Targets**

- ex2-lint

- ex2-openlane

- ex2-openroad

- ex2-klayout

- ex2-cocotb

- ex2-cocotb-gl

To add additional source files to your cipher, just place them into the src/ folder! All files ending in .sv are automatically picked up for the implementation and the simulation.

ex2/src/\*.sv

# **Tapeout**

#### **Final Step**

#### To complete the tapeout:

- Harden your cipher\_peripheral

- · Generate the ROMs for your program

- (Optionally) Update the chip art

- open-flow/tapeout/chip\_art/chip\_art.png

- · Merge everything!

#### **Make Targets**

- tapeout-chip\_art generate the macro for your chip art

- tapeout-rom generate both ROM macros

- Set \$PROGRAM env variable to active program

- tapeout-final perform the final merging of the layouts

- · Cipher, ROM and chip art must be hardened first

- tapeout-klayout open the final layout using KLayout

#### **Set the active \$PROGRAM**

To change the program that is compiled, set the \$PROGRAM environment variable.

To create a new program, just copy the whole folder ex2/sw/hello-world and rename it, for example ex2/sw/cipher-test.

#### This is necessary for:

- ex2-sw

- ex2-cocotb

- ex2-cocotb-gl

- · tapeout-rom

Execute make targets like this:

PROGRAM=cipher-test ex2-cocotb

**General Makefile Targets**

#### \$ make interactive

This command starts the docker container in interactive mode.

You will find yourself in a command prompt and have access to all the tools installed in the docker container.

Normally this should not be necessary for the course, but can be used for troubleshooting.

```

/foss/designs > ls

ex1 ex2 ex2-def LICENSE Makefile README.md tapeout

/foss/designs/ex1 > ls

/foss/designs/ex1 > ls

config.json pins.cfg runs src tb

config.json pins.cfg runs src tb

/foss/designs/ex1/src > ls

clipher.core.sv cipher.core.v

/foss/designs/ex1/src > cd ../../

/foss/designs/ex1/src > cd ../../

/foss/designs > ls

ex1 ex2 ex2-def LICENSE Makefile README.md tapeout

```

#### \$ make gtkwave

This command starts GTKWave using the docker container without a waveform loaded.

With it you can view the simulation results for your cipher.

#### \$ make klayout

This command starts KLayout using the docker container without a design loaded.

Klayout is a capable layout viewer and will be used to visualize the layout of your cipher and the final chip.

**Makefile Targets - Exercise 1**

#### \$ make ex1-lint

Runs verilator in linting mode over your design to detect issues that can lead to problems.

Make sure to fix all warnings. Otherwise this might lead to problems later on.

```

Nerror: exl/src/clpher_core.sv:36:20: Con't find definition of variable: 'test123'

36 | assign tag o = test123;

Merror: exl/src/clpher_core.sv:37:21: Con't find definition of variable: 'test234'

... Suggested alternative: 'test123'

37 | assign busy, o = test124;

Merror: exl/src/clpher_core.sv:38:23; con't find definition of variable: 'test345'

38 | assign finish o = test145;

Merror: Exiting due to 3 error(s)

mohe: '** (Mokefile:22: exl-lint) [enler 1]

```

#### \$ make ex1-openlane

Starts the physical process of hardening cipher\_core using the sky130A PDK.

Actually, OpenLane 2 is used to harden your ciper. OpenLane 2 is the successor to OpenLane.

```

Flansed: 0.000s Nemory: 943.00M

merged" in: skyl38A mr.drc:439

Polygons (raw): 938 (flat) 938 (hierarchical)

Elanced: 8 888s Memoru: 943 88M

outside part" in: skyl38A mr.drc:439

Edges: 0 (flat) 0 (hierarchical)

Elapsed: 0.010s Memory: 943.00M

"space" in: skyl38A mr.drc:441

Edge pairs: 0 (flat) 0 (hierarchical)

Elansed: 8 848s Memory: 959 88M

output" in: sky1384 mr. drc. 441

Edge pairs: 0 (flat) 0 (hierarchical)

Elapsed: 8.000s Memory: 943.00M

"separation" in: skyl38A mr.drc:443

Edge pairs: 0 (flat) 0 (hierarchical)

Elapsed: 0.020s Memory: 959.00M

space" in: sky1384 mr.drc:443

Edge pairs: 0 (flat) 0 (hierarchical)

Elapsed: 0.020s Memory: 943.00M

+" in: sky138A mr.drc:443

Edge pairs: 0 (flat) 0 (hierarchical)

Elansed: 0.000s Memory: 943.00M

output in: skyl38A mr.drc:443

Edge pairs: 0 (flat) 0 (hierarchical)

Flansed: 0.818s Memory: 943.88M

input in: skyl38A mr.drc:447

Polymons (rms): 50570 (flat) 2546 (bigrarchical)

Flansed: 8.818s Memory: 943.88M

enclosing" in: skyl384 mr.drc:449

Classic - Stage 56 - Design Rule Check (KLavout)

```

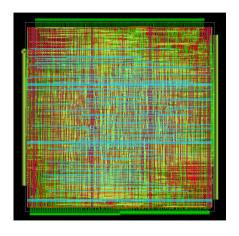

#### \$ make ex1-openroad

Loads the latest stage from "ex1-openlane" into OpenROAD to visualize the design. This can be useful if the hardening process fails due to routing congestion etc.

To save an image of your design execute "save\_image image.png" in the tcl command line.

#### \$ make ex1-klayout

Opens the layout of your design from ex1/results in Klayout.

To save a high-resolution image, open:

Macros → Macro Development

Then execute in the console:

RBA::Application.instance

.main\_window.current\_view

.save\_image("image.png",2000,2000)

#### \$ make ex1-cocotb

Runs RTL simulation of your design using cocotb as the testbench environment.

You can write your testbench in Python under ex1/tb/.

For RTL simulation, Verilator is used as the simulator.

#### \$ make ex1-cocotb-gl

Runs GL simulation of your design using cocotb as the testbench environment.

The same testbench under ex1/tb/ is used with \$GL set to 1.

For GL simulation, Icarus Verilog is used as the simulator.

#### \$ make ex1-gtkwave

After running RTL or GL simulation for exercise 1 the resulting waveform "dump.fst" is saved under ex1/tb/sim\_build.

This make target starts GTKWave with "dump.fst" loaded.

**Makefile Targets - Exercise 2**

#### \$ make ex2-lint

Runs verilator in linting mode over your design to detect issues that can lead to problems.

Make sure to fix all warnings. Otherwise this might lead to problems later on.

#### \$ make ex2-openlane

Starts the physical process of hardening cipher\_core using the sky130A PDK.

Actually, OpenLane 2 is used to harden your ciper. OpenLane 2 is the successor to OpenLane.

```

September 1, 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 1975 - 197

```

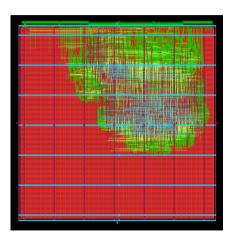

#### \$ make ex2-openroad

Loads the latest stage from "ex2-openlane" into OpenROAD to visualize the design. This can be useful if the hardening process fails due to routing congestion etc.

To save an image of your design execute "save\_image image.png" in the tcl command line.

#### \$ make ex2-klayout

Opens the layout of your design from ex2/results in Klayout.

To save a high-resolution image, open:

Macros → Macro Development

Then execute in the console:

RBA::Application.instance

.main\_window.current\_view

.save\_image("image.png",2000,2000)

#### \$ make ex2-cocotb

Runs RTL simulation of your design using cocotb as the testbench environment.

You have to write your own program under /ex2/sw/. Set \$PROGRAM to the active program e.g. hello-world.

For RTL simulation, Verilator is used as the simulator.

#### \$ make ex2-cocotb-gl

Runs GL simulation of your design using cocotb as the testbench environment.

Same as ex2-cocotb, but \$GL is set to 1 and the gate level files for cipher\_peripheral are used.

For GL simulation, Icarus Verilog is used as the simulator.

#### \$ make ex2-gtkwave

After running RTL or GL simulation for exercise 2 the resulting waveform "dump.fst" is saved under ex2/tb/sim\_build.

This make target starts GTKWave with "dump.fst" loaded.

**Makefile Targets - Tapeout**

#### \$ make tapeout-chip\_art

Starts a Klayout Python script to convert the PNG image under tapeout/chip\_art/chip\_art.png to .gds. A tcl script for Magic creates a .lef file.

Feel free to change the image, but make sure to keep the resolution.

```

Creating macro of size 1808 µm x 580 µm

Magic 8.3 revision 452 - Compiled on Mon Feb 12 83:85:47 PM CFT 2824

Starting magic under Tcl interpreter

Using the terminal as the console.

Using NULL graphics device.

Processing system .magicrc file

Sourcing design .magicrc for technology skyl30A ...

2 Magic internal units = 1 Lambda

Input style sky130(): scaleFactor=2, multiplier=2

The following types are not handled by extraction and will be treated as non-electrical types

Scaled tech values by 2 / 1 to match internal grid scaling

Loading skyl38A Device Generator Menu

Loading "ads2lef.tcl" from command line

Input style sky130(vendor): scaleFactor=2, multiplier=2

CIF input style is now "skyl30(yendor)"

Warning: Calma reading is not undoable! I hope that's OK

Library written using GDS-II Release 6.0

Library mame: LTB

Reading "chin art"

Generating LEF output chip art.lef for cell chip art:

Diagnostic: Write LEF header for cell chip art

Diagnostic: Writing LEF output for cell chip art

```

Diagnostic: Scale value is 0.005080

#### \$ make tapeout-rom

Starts OpenRAM (or you could say OpenROM) to create a ROM macro for your program.

Set \$PROGRAM to the active program e.g. hello-world.

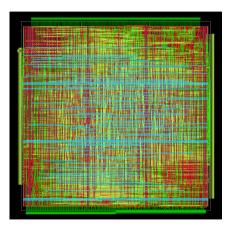

#### \$ make tapeout-final

The final step to complete tapeout!

This target calls a Klayout Python script to merge the layouts of your cipher, the ROMs and the chip\_art with the pre-hardened chip.

Congratulations, your design is finished!

```

Replacing instance CH cipher wropper ex2 with GDS ex2/results/gds/cipher wropper ex2.gds

Replacing instance CH skyll@ row Abbyte 32_inst0 gds

replacing instance CH skyll@ row Abbyte 32_inst0 gds

replaced in the replaced replaced

```

#### \$ make tapeout-klayout

Opens the layout of your design chip\_tapeout.gds in Klayout.

To save a high-resolution image, open:

Macros → Macro Development

Then execute in the console:

RBA::Application.instance

.main\_window.current\_view

.save\_image("image.png",2000,2000)

## Open Source Tools

#### Verilator

Verilator is a free and open-source software tool which converts Verilog to a cycle-accurate behavioral model in C++ or SystemC. Verilator is the fastest Verilog/SystemVerilog simulator.

Website: https:

//www.veripool.org/verilator/

### **Icarus Verilog**

Icarus Verilog is an implementation of the Verilog hardware description language compiler that generates netlists in the desired format. It supports the 1995, 2001 and 2005 versions of the standard, portions of SystemVerilog, and some extensions.

Repository: https:

//github.com/steveicarus/iverilog

#### cocotb

cocotb is an open source coroutine-based cosimulation testbench environment for verifying VHDL and SystemVerilog RTL using Python.

Website: https://www.cocotb.org/

#### **GTKWave**

GTKWave is an open source waveform viewer and can read various formats such as fst and vcd files.

#### Repository:

https://github.com/gtkwave/gtkwave

#### **OpenROAD**

OpenROAD's unified application implementing an RTL-to-GDS Flow.

Repository: https://github.com/

The-OpenROAD-Project/OpenROAD

Documentation: https://openroad.

readthedocs.io/en/latest/

#### OpenLane 2

The next generation of OpenLane, rewritten from scratch with a modular architecture

Repository: https:

//github.com/efabless/openlane2

Documentation: https://openlane2.

readthedocs.io/en/latest/

#### **Magic VLSI Layout Tool**

Magic is a venerable VLSI layout tool, written in the 1980's at Berkeley by John Ousterhout. With well thought-out core algorithms, Magic is a powerful yet simple tool for circuit layout and validation.

Repository: https:

//github.com/RTimothyEdwards/magic

#### **KLayout**

KLayout chip mask layout viewing, editing and more. It provides an extensive Ruby and Python API.

Website: https://www.klayout.de/

#### **OpenRAM**

An open-source static random access memory (SRAM) compiler.

Website: https://openram.org/

Repository:

https://github.com/VLSIDA/OpenRAM

#### **Further Links**

- IAIK Open Flow

- Skywater SKY130 PDK

- GlobalFoundries GF180MCU PDK

- IHP SG13G2 PDK

- Qflow

- Coriolis

- LunaPnR

- Place & route on silicon

- Tiny Tapeout

# Digital System Design IAIK Open Flow

**DSD** Team

06.03.2024

Digital System Design Graz University of Technology